Digital Logic Design with FPGA

### **Design Flow with Quartus**

Foundations

### Outline

- Modeling digital systems

- Typical design flow with HDL

- Intel PLD design flow

- Quartus Prime software

- □ Project flow

- Design entry

- Compilation tools

- □ Verification of results

# Digital system vs. Digital device

Digital circuit...

equipment that performs functions using an appropriate structure of electronic components

### Digital system ...

a set of digital circuits, contains at least one programmable processor, performs a significant part of its functions by means of software executed by this processor

### **Embedded system**

An embedded system is a microprocessor system built into any technical device, performing specific control, measurement, signal processing functions, etc.,

- Basic elements of an embedded system:

- □ Microcontroller / microprocessor

- □ Application-specific hardware (ASIC/FPGA)

- □ Application software

- □ Real-time operating system (RTOS)

- New design considerations:

- □ system level design,

- □ co-creation of hardware and software (H/S Codesign)

# **Evolution of ASIC to SoC/SoPC**

Technological possibilities allow you to fit in one integrated circuit:

- processor (several processors, e.g. signal processor, microcontroller, many cores with different parameters)

- □ memory (ROM & SRAM, in specific processes Flash memory, "e"-DRAM)

- □ standard communication blocks (e.g. I2C or USB controller)

- □ application-specific logic subcircuits (ASSP)

- □ mixed and analog circuits (e.g. ADC and DAC converters)

- □ mechanical microsystems (e.g. MEMS sensors)

Programmable devices also now contain logical resources enabling the implementation of systems in a single package (including embedded processors) -> SoPC, PSoC, APSoC

# **Modeling Digital Systems**

- Simulation and modeling at the system level

- □ performance analysis

- Behavior specification at the algorithmic level

- preliminary functional verification of algorithms

- □ division into hardware and software

- □ high-level synthesis

- Simulation behavioral models of standard elements

- Functional simulations at the system/package level

- 🗆 full

- □ bus

- Synthesizable models at the RTL (register transfer level)

- □ full functional specification of the project

- Model of the system environment (testbench)

- Simulation models of library cells from integrated circuit manufacturers (VITAL standard)

- □ time verification of ASIC/FPGA systems

#

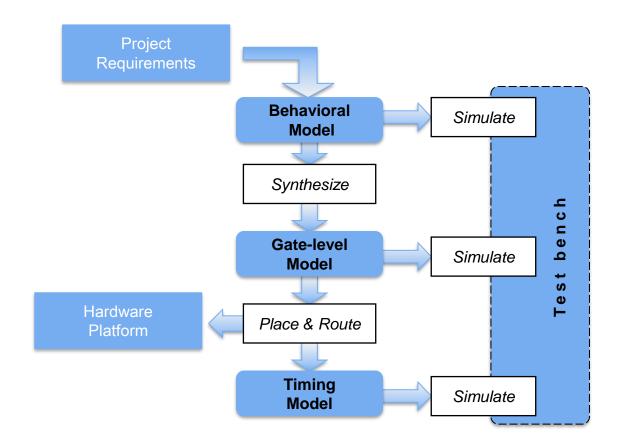

# **Typical design flow with HDL**

### **Design stages**

- Specification / design entry

- Synthesis

- □ implementation of functions based on component (library) elements

- □ optimization (e.g. logical minimization)

- □ generation (physical implementation of the structure)

- Analysis

- $\Box$  simulation validation, regression tests

- □ formal verification (equivalence of two representations)

- verification of design rules

- Implementation

- □ from SSI / MSI / LSI / VLSI catalog items (memory / ASSP)

- □ programmable systems (FPGA / CPLD)

- □ specialized systems (ASIC)

- □ embedded systems (traditional and integrated SoC)

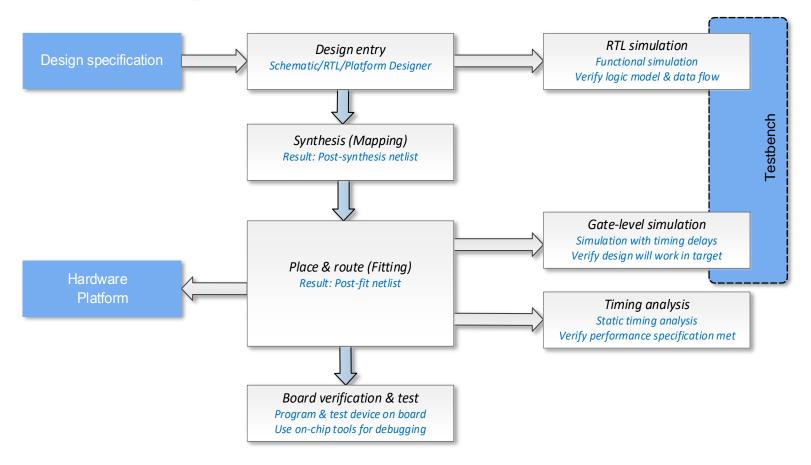

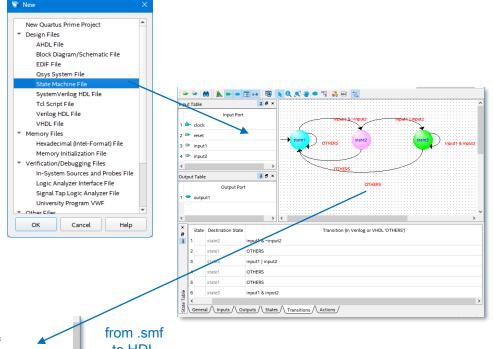

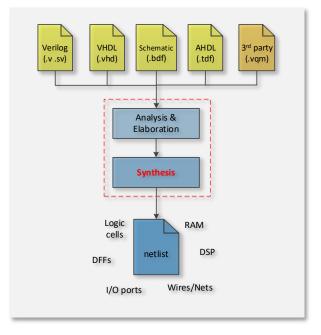

### **Intel PLD Design Flow**

### **Intel Quartus Prime**

- Fully-integrated development tool

- □ Multiple design entry methods

- □ Logic synthesis

- □ Place & route

- □ Device programming

- Simulation

- Supports standard HDL simulation tools

- □ Includes ModelSim(Questa)-Intel FPGA Starter Edition tool

- □ Optional upgrade to ModelSim(Questa)-Intel FPGA Edition tool

### Intel' Quartus' Prime

Design Software

### Lite Edition (LE)

Standard Edition (SE)

### **Pro Edition (PE)**

### **Quartus Prime Software**

- Lite Edition (LE)

- Supported families:

Cyclone V, IV

MAX 10, V, II

- □ No license file required

- Standard Edition (SE)

- Supported families: Stratix V, IV

Arria 10, V, II

Cyclone V, IV

MAX 10, V, II

- □ License file required

- Pro Edition (PE)

- Supported families: Stratix 10 Arria 10

- □ License file required

### Intel' Quartus' Prime

Design Software

### Lite Edition (LE)

**Standard Edition (SE)**

### **Pro Edition (PE)**

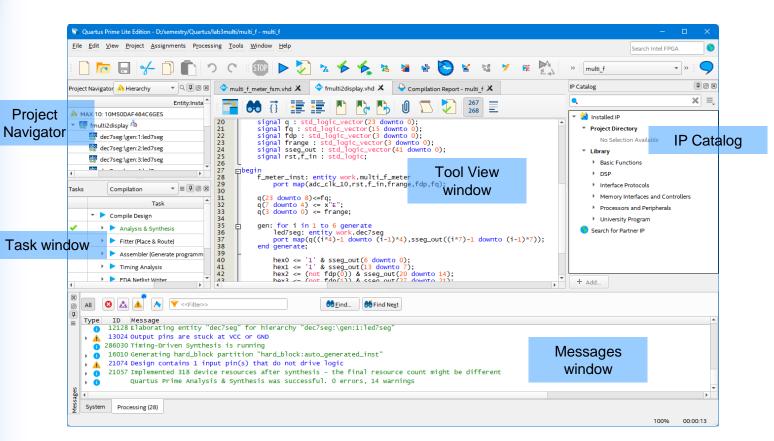

### **Quartus Prime GUI**

### **Quartus Prime Help System**

| Quartus Prime Standard Edit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ition Help version 18.1                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CG 💧                                                                                                                                                                             |

| Contract of the Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Set Clock Groups Dialog Box (set_clock_groups)                                                                                                                                   |

| Welcome to the Quartus <sup>®</sup> Prime Standard Editio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Tou access this dated box by clicking Set Clock Groups on the Constraints menu in                                                                                                |

| About Simulating Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TimeQuest Timing Analyzer.                                                                                                                                                       |

| Running Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Allows you to specify which clocks in the design are unrelated.                                                                                                                  |

| Control of the second s | The TimeQuest analyzer analyzes all clocks in a design as related, by default. The S<br>Clock Groups dialog box (and the set clock groups SDC command) allows you                |

| Set Clock Groups Dialog Box (set_clock_groups<br>Set Clock Latency Dialog Box (set_clock_latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | and the second standard standards have see the second standard standards                                                                                                         |

| Set Clock Uncertainty Dialog Box (set_clock_uncertainty Box (set_clock_unc    |                                                                                                                                                                                  |

| Set False Path Dialog Box (set_false_path)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ideal clock sources. Exclusive clocks (-exclusive) are not active at the same time,<br>such as multiplexed clocks. The TimeQuest analyzer treats both types of clocks as if      |

| 🗟 Set Input Delay Dialog Box (set_input_delay)<br>🗟 Set Output Delay Dialog Box (set_output_delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | were the same                                                                                                                                                                    |

| Set Output Delay Dialog Box (set_output_delay) Set Maximum Delay Dialog Box (set_max_delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

| Set Minimum Delay Dialog Box (set_min_delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | () command for paths from each clock domain in every group to each clock domain in                                                                                               |

| Set Multicycle Path Dialog Box (set_multicycle_p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _path)                                                                                                                                                                           |

| Integrating Other EDA Tools Integration Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | might define in the future.                                                                                                                                                      |

| About Integrating Other EDA Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The following sections provide more information about specifying options for this                                                                                                |

| Preparing for EDA Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | constraint:                                                                                                                                                                      |

| Running EDA Simulators W Simulation Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Group 1 (-group):                                                                                                                                                                |

| C Active-HDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Allows you to specify the clocks to which the constraint applies. You can use the Nam                                                                                            |

| Performing a Simulation of a Verilog HDL Designation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Cleake ensetified in this group are sut from the cleake ensetified in the Crown 2 hour                                                                                           |

| Performing a Simulation of a VHDL Design with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ith the Active-HDL Software                                                                                                                                                      |

| ModelSim ModelSim-Altera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Group 2 (-group):                                                                                                                                                                |

| <ul> <li>ModelSinPAtera</li> <li>Incisive Enterprise Simulator</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Allows you to specify the clocks to which the constraint applies. You can use the Nam                                                                                            |

| 🔷 QuestaSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Finder () and the get_clocks option to build a <u>collection Definition</u> of clocks.                                                                                           |

| Riviera-PRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Clocks specified in this group are cut from the clocks specified in the Group 1 box. If<br>leave this setting blank, then the clocks in the Group 1 box are cut from every other |

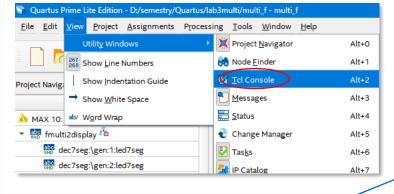

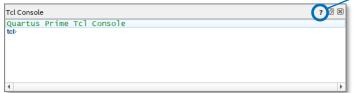

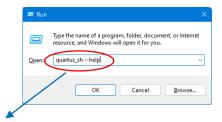

### **Tcl Console**

Enter and execute Tcl commands directly in the GUI

View menu -> Utility Windows -> Tcl Console

- Execute from command-line using Tcl shell

- $\Box$  quartus\_sh -s

C:\<install dir>\quartus\bin64\quartus\_sh --qhelp

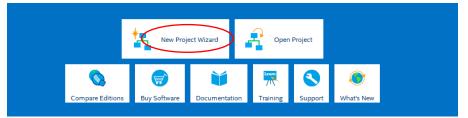

# **Quartus Prime Design Software**

- Quartus project

- □ Collection of related design files & libraries

- □ Must have a designated top-level entity

- □ Target a single device

- □ Store settings in settings file (.qsf)

- □ Compiled netlist information stored in **qdb** folder in project directory

- Create new projects with New Project Wizard

Can be created using Tcl scripts

Tcl: roject\_new <project\_name>

# **Add Files in Project**

- Add design files

- □ VHDL

- □ Verilog

- □ SystemVerilog

- □ EDIF

- □ VQM

- □ Intel® Quartus® Prime software IP

- □ Platform Designer

| elect the design files yo<br>lote: you can always ado |                   |            | oject. Click Add All to add all desig<br>later | gn files in the project dire | ctory to the proj | ject.            |

|-------------------------------------------------------|-------------------|------------|------------------------------------------------|------------------------------|-------------------|------------------|

| ile name:                                             | a design mes to a | ie project |                                                |                              |                   | <u>A</u> dd      |

| ٩                                                     |                   |            |                                                |                              | ×                 | Add A <u>l</u> l |

| File Name                                             | Туре              | Library    | Design Entry/Synthesis Tool                    | HDL Version                  |                   | Remove           |

| sw2display.vhd                                        | VHDL File         |            |                                                | Default                      |                   | _                |

| encoder.vhd                                           | VHDL File         |            |                                                | Default                      |                   | <u>U</u> p       |

| demux.vhd                                             | VHDL File         |            |                                                | Default                      |                   | Down             |

| dec7seg.vhd                                           | VHDL File         |            |                                                | Default                      |                   | Down             |

|                                                       |                   |            |                                                |                              |                   | Properties       |

Tcl: set\_global\_assignment -name VHDL\_FILE <filename.vhd>

Add library paths

- □ User libraries

- □ Intel® FPGA Intellectual Property (IP) library

- □ Pre-compiled VHDL packages

Tcl: set\_global\_assignment -name USER\_LIBRARIES <library\_path\_name>

### **Device & Family Selection**

Choose device family & family category

| Device                                       |                       |           |                        |               |                        |                                                       |  |  |

|----------------------------------------------|-----------------------|-----------|------------------------|---------------|------------------------|-------------------------------------------------------|--|--|

| Device Board                                 |                       |           |                        |               |                        |                                                       |  |  |

| elect the family and de                      |                       | · ·       |                        | mmand on t    | he Tools m             | enu.                                                  |  |  |

| o determine the versio                       | on of the Quartus P   | rime soft | ware in which yo       | our target de | vice is supp           | orted, refer to the <u>Device Support List</u> webpag |  |  |

| evice family                                 |                       |           |                        | Show in 'A    | Available de           | vices' list                                           |  |  |

| Eamily: MAX 10 (DA/DD/DF/DC/SA/SC/SL)        |                       |           |                        |               | e:                     | FBGA 💌                                                |  |  |

| Dev <u>i</u> ce: MAX 10 DA 🔹                 |                       |           |                        |               | Pin <u>c</u> ount: 484 |                                                       |  |  |

| Target device                                |                       |           |                        | Core sp       | eed grade:             | 8 🔹                                                   |  |  |

| ○ <u>A</u> uto device selected by the Fitter |                       |           | Name fi                | Name filter:  |                        |                                                       |  |  |

| • Specific device se                         | elected in 'Available | devices'  | list                   | S <u>h</u> o  | w advanced             | devices                                               |  |  |

| ◯ <u>O</u> ther. n/a                         |                       |           | Device and Pin Options |               |                        |                                                       |  |  |

| vailable devices:                            |                       |           |                        |               |                        |                                                       |  |  |

| Name                                         | Core Voltage          | LEs       | Total I/Os             | GPIOs         | Memory                 | Bits Embedded multiplier 9-bit eleme                  |  |  |

| 10M08DAF484C8G                               | 1.2V                  | 8064      | 250                    | 250           | 387072                 | 48                                                    |  |  |

| 10M08DAF484C8GES                             | 1.2V                  | 8064      | 250                    | 250           | 387072                 | 48                                                    |  |  |

| Migration Devices 0                          | migration devices     | selected  |                        |               |                        |                                                       |  |  |

|                                              |                       |           |                        | `₩ Bu         | uy Software            | OK Cancel Help                                        |  |  |

|                                              |                       |           |                        |               |                        | IV Neleccie of femiles r                              |  |  |

Tcl: set\_global\_assignment -name FAMILY "device family name"

Tcl: set\_global\_assignment -name DEVICE <part\_number>

### **Opening a Project**

#### From File menu

#### From Recent Project

#### Recent Projects

- A multi\_f.qpf (D:/semestry/Quartus/lab3multi/multi\_f.qpf)

- B proj\_opty.qpf (D:/semestry/Quartus/proj\_opty/proj\_opty.qpf)

- div\_std.qpf (D:/semestry/Quartus/sync\_design/div\_std.qpf)

- A async\_counter\_2b.qpf (D:/semestry/Quartus/seq\_circuits/async\_counter\_2b.qpf)

#### Double-click .qpf file

Tcl script

Tcl: project\_open <project\_name>

# **Quartus Prime Project Files**

- Project File (.qpf)

- □ Intel Quartus Prime software version

- Time stamp

- □ Active revision(s)

- Defaults File (.qdf)

- Stores project setting & assignment defaults for new project revisions

- crevision\_name>\_assignment\_defaults.qdf

- Settings File (.qsf)

- □ Stores all settings & assignments except timing

- Uses Tcl syntax

- □ Can be edited manually by user

- Synopsys Design Constraints (.sdc)

- □ Contains timing constraints

- qdb folder

- □ Contains compiled design information

- output\_files folder (customize location/name in project settings)

- □ Generated compilation report files

- Programming files generated by the Assembler

| 26 | QUARTUS VERSION = "23.1"         |

|----|----------------------------------|

| 27 | DATE = "21:27:21 March 04, 2024" |

| 28 |                                  |

| 29 | # Revisions                      |

| 30 |                                  |

| 31 | PROJECT_REVISION = "sw2display"  |

# **Constraint Files & Assignment Priority**

- Settings File (.qsf)

- □ Highest priority

- □ Assignments always used from here first

- Revision-specific .qdf file located in project directory

- □ <revision\_name>\_assignment\_defaults.qdf

- □ Created automatically in the project directory when a revision is opened in another version of Quartus Prime software

- .qdf located in project directory

- □ assignment\_defaults.qdf

- □ Created automatically in project directory when project archived & restored

- .qdf located in Intel Quartus Prime Design Software bin64 directory

- □ Lowest priority

- □ Assignments only used if not found in higher priority files

### **Project Archive & Restore**

- Archive Creates 2 files

- Compressed Quartus Prime Design Software Archive File (.qar)

- Includes design files, .qpf file, & .qsf file(s)

- Option to include databases

- Creates local .qdf file for archive

- □ Archive activity log (.qarlog)

- Tcl: project\_archive <project\_name>

- Restore decompresses .qar into specified directory

- Paths/directory structures to referenced files/libraries *outside* project directory must also be restored

- □ Recreated in restore location based on nearest common *parent directory*

- □ Example of referenced file paths in restored project destination:

- <destination folder>/drive/C/<entire path to all files in project directory>

- <destination folder>/drive/H/<path to file(s) referenced on original H drive>

**Tcl:** project\_restore <archive\_file>

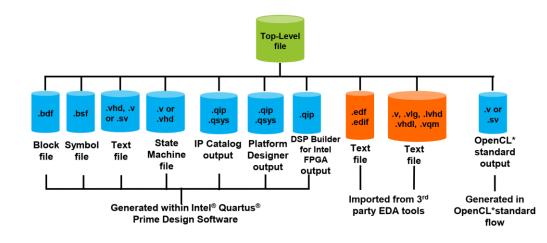

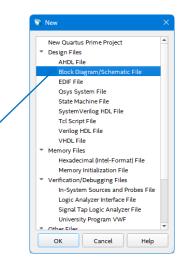

### **Design entry methods**

- Quartus Prime design entry

- Text editor

- VHDL

- Verilog or SystemVerilog

- Schematic editor

- Block Diagram File

- System editor

- Platform Designer

- □ State machine editor

- HDL from state machine file

- □ Memory editor

- HEX

- MIF

- 3rd-party EDA tools

- □ EDIF 2 0 0

- □ Verilog software Mapping (.vqm)

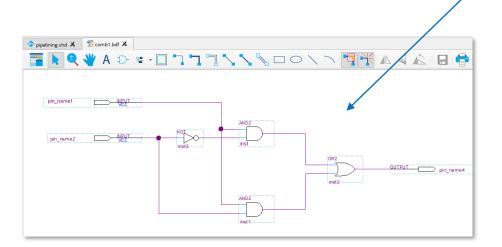

### **Schematic Editor**

- Full-featured schematic design capability

- Schematic Editor uses

- □ Create simple test designs to understand the functionality of an Intel FPGA IP: PLL, LVDS I/O, memory, etc...

- □ Create top-level schematic for easy viewing & connection

- □ Convert between schematic .bdf, block symbol .bsf, and HDL files

### **State Machine Editor**

- Create state machines in GUI

- Manually by adding individual states, transitions, and output actions

- Automatically with State Machine Wizard (Tools menu & toolbar)

- Generate state machine HDL code

- VHDL, Verilog, SystemVerilog

- Automatically added to project

- Required for use

307 333 390 442 433 445 467 449 552 555 556 57 58 506 122 664 656 67 always @(posedge clock) Ξ begi (clock) begin fstate <= req\_fstate; ond always @(fstate or reset or input1 or input2) Ξ begi if (reset) begin reg\_fstate <= state1; end else begin case (fstate) state1: begin ((input1 & ~(input2)))

reg fstate <= state2;</pre> else reg fstate <= state1: end eno state2: begin if ((input1 | input2)) reg\_fstate <= state3; else reg\_fstate <= state1;</pre> end state3: begin if ((input1 & input2)) roo fstate <= stat reg\_fstate <= state3; else req\_fstate <= state1;

to HDL

source: https://www.intel.com/content/www/us/en/support/programmable/support-resources/design-software/fpga-development-tools-support.html

### **Intel MAX10 Design Flow**

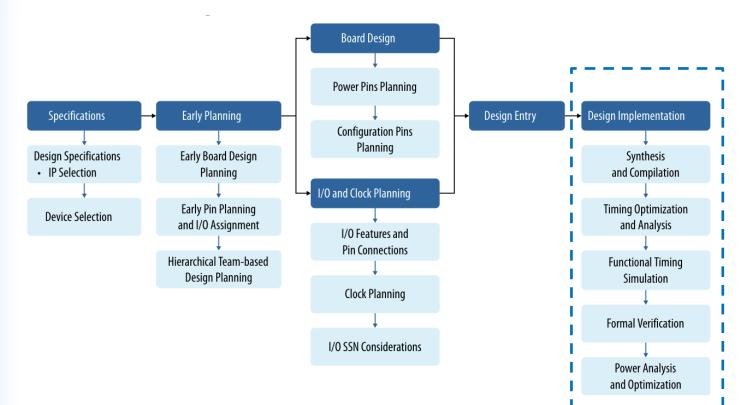

### **Design compilation**

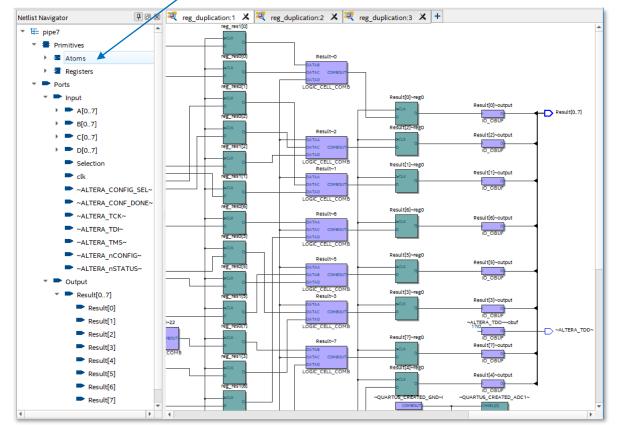

#### **Synthesis**

- Translates HDL source files into an atom netlist

- Generates an advanced hierarchical database

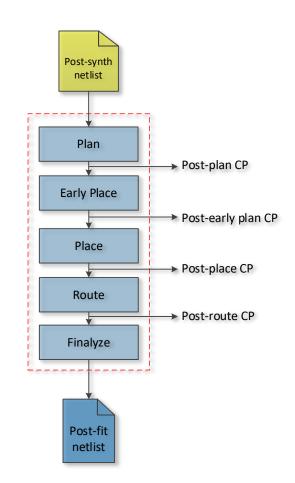

# **Design compilation - Fitter**

- Advanced place & route engine for finding a valid "solution" in a "reasonable" amount of time

- Consists of 4 stages

- □ Plan

- Periphery (I/O) placement and routing, clock resource selection

- □ Early Place

- Early assignment of core logic to device resources

- More pessimistic results within 20% of final routed results

- □ Place

- Core resource placement (logic elements, registers, DSP, RAM)

- □ Route

- Core routing connections made

- □ Finalize

- Post-routing optimizations

- Stages can be all run or individually

- □ End of running each stage referred to as a checkpoint (CP)

- Prior stages must be complete before running later stages

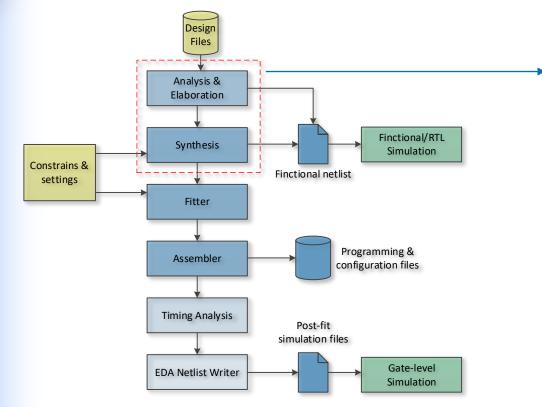

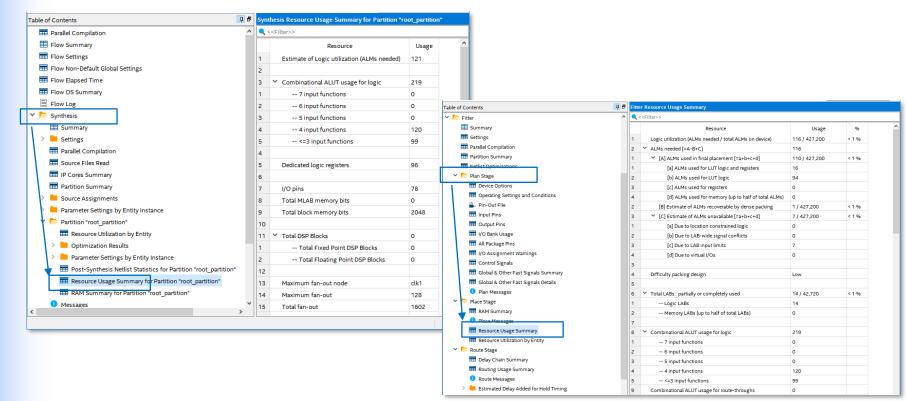

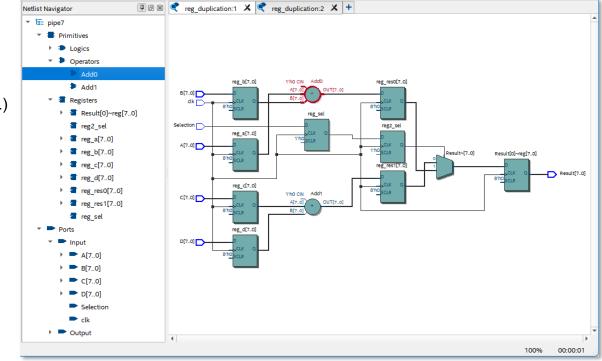

# **Compilation Results**

- Quartus Prime Design Software graphical tools available for

- Understanding design processing

- □ Verifying correct design results

- Debugging incorrect results

- Compilation Report

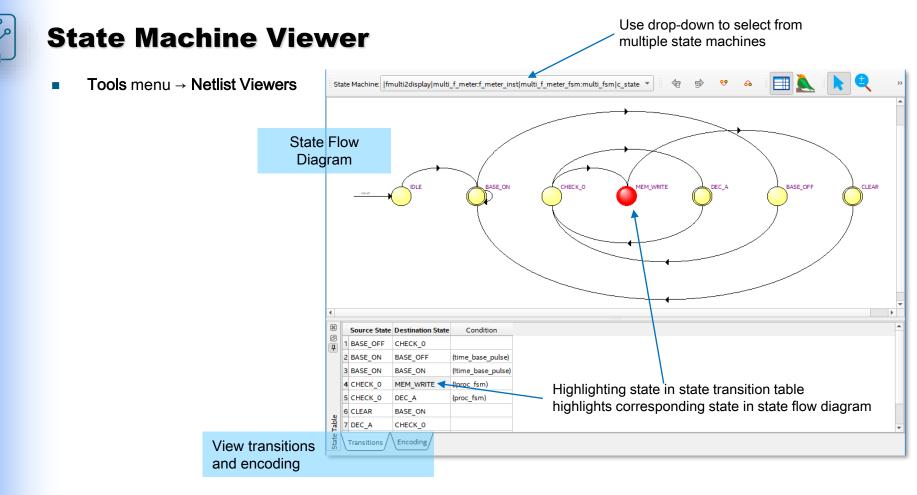

- Viewers

- RTL Viewer

- □ Technology Map Viewer

- □ State Machine Viewer

- Chip Planner

| Fable of Contents                                   |   | Flow Summary                                     |                                                |  |  |

|-----------------------------------------------------|---|--------------------------------------------------|------------------------------------------------|--|--|

| Flow Settings                                       | - | < <filter>&gt;</filter>                          |                                                |  |  |

| Flow Non-Default Global Settings                    |   | Flow Status                                      | Successful - Thu May 9 11:11:04 2024           |  |  |

| I Flow Elapsed Time                                 |   | Quartus Prime Version                            | 23.1std.0 Build 991 11/28/2023 SC Lite Edition |  |  |

| Elow OS Summary                                     |   | Revision Name                                    | reg_duplication                                |  |  |

| Flow Log                                            |   | Top-level Entity Name                            | pipe7                                          |  |  |

| Analysis & Synthesis                                |   | Family                                           | MAX 10                                         |  |  |

| I Summary                                           |   | Device                                           | 10M08DAF484C8G                                 |  |  |

| Settings                                            |   | Timing Models                                    | Final                                          |  |  |

| Parallel Compilation                                |   | Total logic elements                             | 26 / 8,064 ( < 1 % )                           |  |  |

| Source Files Read                                   |   | Total registers                                  | 58                                             |  |  |

| E Resource Usage Summary                            |   | Total pins                                       | 42 / 250 ( 17 % )<br>0                         |  |  |

|                                                     |   | Total virtual pins                               | -                                              |  |  |

| Resource Utilization by Entity                      |   | Total memory bits                                | 0/387,072(0%)                                  |  |  |

| Optimization Results                                |   | Embedded Multiplier 9-bit elements<br>Total PLLs |                                                |  |  |

| Post-Synthesis Netlist Statistics for Top Partition |   | UFM blocks                                       | 0/2(0%)<br>0/1(0%)                             |  |  |

| Elapsed Time Per Partition                          |   | ADC blocks                                       | 0/1(0%)                                        |  |  |

| Messages                                            |   | ADC DIOCKS                                       | 0/1(0%)                                        |  |  |

| 🔻 🦰 Fitter                                          |   |                                                  |                                                |  |  |

| Summary                                             |   |                                                  |                                                |  |  |

| Settings                                            |   |                                                  |                                                |  |  |

| === Parallel Compilation                            |   |                                                  |                                                |  |  |

| III Netlist Optimizations                           |   |                                                  |                                                |  |  |

| Incremental Compilation Section                     |   |                                                  |                                                |  |  |

| Pin-Out File                                        |   |                                                  |                                                |  |  |

| Resource Section                                    |   |                                                  |                                                |  |  |