Digital Logic Design with FPGA

### **Design Flow with Quartus**

Simulation & HW Debug

### Outline

- Modeling digital systems

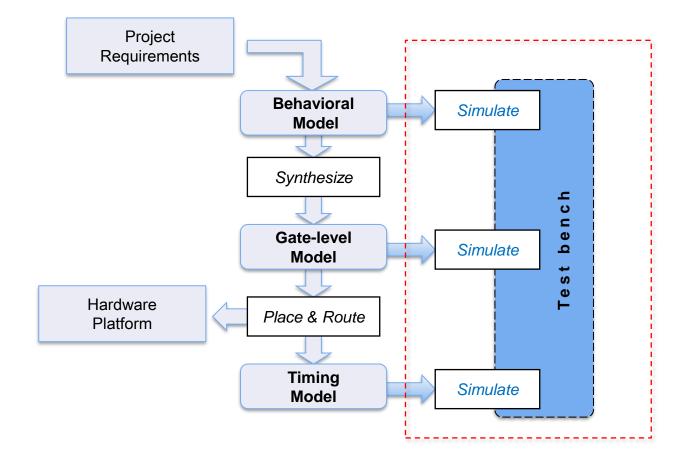

- Simulation in typical design flow

- □ Simulation tools

- □ Timing simulation

- Hardware debug

- □ In-System Sources and Probes (ISSP)

- □ Signal Tap Internal Analyzer

# **Modeling Digital Systems**

- Simulation and modeling at the system level

- □ performance analysis

- Behavior specification at the algorithmic level

- preliminary functional verification of algorithms

- □ division into hardware and software

- □ high-level synthesis

- Simulation behavioral models of standard elements

- Functional simulations at the system/package level

- 🗆 full

- □ bus

- Synthesizable models at the RTL (register transfer level)

- □ full functional specification of the project

- Model of the system environment (testbench)

- Simulation models of library cells from integrated circuit manufacturers (VITAL standard)

- □ time verification of ASIC/FPGA systems

# Simulation in typical design flow

### Simulation

- Provide results that are impossible to measure in HW prototype

- Include wide range of analyses

- Reduce development costs

- Minimize time-to-market

- Delivering visibility of all signals in design

- Designer has to create stimulus that matches device behavior

- Can take very long time to run for large designs

|             | clk_10M           | 1                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|-------------|-------------------|------------------|-------------|-------|-------------|--------------|----------------|----------|---------|---------------|-----------|---------------|------|----------|----------|-------|---------|----------|-----------|---------|------------------|----------|

| 3           |                   | 0                |             |       |             |              |                |          |         |               |           |               | -    |          |          |       |         |          |           |         |                  |          |

|             | f_in              | 0                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | f_range           | 4'h0             | 3           |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           | 0       |                  |          |

| <b>⊡-</b> ◆ |                   | 4'h1             | 2           |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           | 1       |                  |          |

| 🗉 🔷         |                   | 16'h0345         | 1234        |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           | 0345    |                  |          |

| - 🗇         | time_base_rst     | 1                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | time_base_on      | 0                |             |       | L           |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | next_address      | 1                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | freq_counter_full | 0                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | time_base_pulse   | 0                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | memory_en         | 0                |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

|             | fsm_address       | 4'h2             | 8           |       |             |              |                | <u>7</u> |         | <u>[6</u>     |           | <u>[5</u>     |      | 4        |          | 3     |         | 2        |           |         | 8                |          |

|             | counter_out       |                  | {0} {0} {0} |       | } {3} {4} { | 5}           |                |          |         |               |           |               |      |          |          |       |         |          |           |         | <u> {{0} }</u> { |          |

|             |                   |                  | 00000034    |       | r.          |              |                |          |         | -             |           |               |      |          |          |       |         |          |           |         | <u>1000 10</u>   |          |

|             | 💫 c_state         |                  | BASE ON     |       |             |              |                |          |         |               |           |               |      | CHECK 0  |          |       |         |          |           |         | BASE ON          |          |

| <u>~</u>    | n_state           | BASE_ON          | BASE ON     | [BASE | CHECK 0     | <u>DEC A</u> | <u>CHECK 0</u> | DEC A    | CHECK 0 | <u>IDEC A</u> | CHECK 0   | <u>IDEC A</u> | CHEC | DEC A    | (CHECK 0 | DEC A | CHECK 0 | (MEM     | CLEAR     | BASE ON |                  |          |

|             |                   |                  |             |       |             |              |                |          |         |               |           |               |      |          |          |       |         |          |           |         |                  |          |

| 🗠 📰 📀       | Now               | 4000005000000 ps | 1.1         | 1 1   | 1 1         | 30000024     | 00000 ps       | 1 1      | 1 1     | 30000028      | 300000 ps | 1 1           |      | 30000032 | 00000 ps | 1 1   | 1.1     | 30000036 | 500000 ps | 1.1     | l 1 1            | 30000040 |

. . .

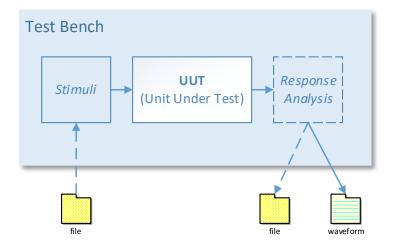

### **HDL Testbench**

- Testbench is a specific design unit described in HDL

- It has no ports and is intended to simulate the designed device (UUT)

- Defines forces (stimuli) and how to interpret simulation results

- Creating a testbench:

- □ written "by hand" by the designer

- generated automatically using graphic editors based on the description of UUT ports

## **HDL Testbench**

| 6        | library IEEE;                                                                                                |

|----------|--------------------------------------------------------------------------------------------------------------|

| 7        | use IEEE.STD LOGIC 1164.ALL;                                                                                 |

| 8        | use std.env.all;                                                                                             |

| 9        |                                                                                                              |

| 10       | Entity d cntr4ceo tb is                                                                                      |

| 11       | generic(T: time:= 1 ns);                                                                                     |

| 12       | end entity d cntr4ceo tb;                                                                                    |

| 13       |                                                                                                              |

| 14       | architecture behav of d cntr4ceo tb is                                                                       |

| 15       | signal clk,rst: std logic := '0';                                                                            |

| 16       | signal ce, ceo, tc : std logic;                                                                              |

| 17       | signal q: std logic vector(3 downto 0);                                                                      |

| 18       |                                                                                                              |

| 19       | constant PERIOD : delay_length := 20*T; Stimulus definition                                                  |

| 20       | Stilluids delinition                                                                                         |

| 21       | procedure clk_gen(signal s: out std_logic; period: delay_length := 10 ns) is                                 |

| 22       | H begin                                                                                                      |

| 26       |                                                                                                              |

| 27       | procedure pulse (signal s: out std logic; Hpulse,Lspace: delay length) is                                    |

| 28       | + i begin                                                                                                    |

| 32       |                                                                                                              |

| 33       | procedure stop after falling edge(signal trig: in std logic; delay: delay length := 0 ns) is                 |

| 34       | + begin                                                                                                      |

| 41       |                                                                                                              |

| 42       | procedure stop after Nfalling edge(signal trig: in std logic; delay: delay length := 0 ns; N: natural:=2) is |

| 44       | begin                                                                                                        |

| 57       |                                                                                                              |

| 58       | Degin                                                                                                        |

| 59       |                                                                                                              |

| 60       | UUT: entity work.d cntr4ceo                                                                                  |

| 61       | <pre>i port map(clk,rst,ce,tc,ceo,q);</pre>                                                                  |

| 62       |                                                                                                              |

|          | pulse (ce, 105*PERIOD, 2*PERIOD);                                                                            |

| 63       | pulse (rst, 2*PERIOD, 12*PERIOD);   Stimulus run                                                             |

| 64       | puise(rst, 2*PERIOD); 1                                                                                      |

| 65       | <pre>clk_gen(clk_PERIOD);</pre>                                                                              |

| 66       | <pre>stop_after_Nfalling_edge(ceo,PERIOD,5);</pre>                                                           |

| 67<br>68 |                                                                                                              |

| 00       | end architecture behav:                                                                                      |

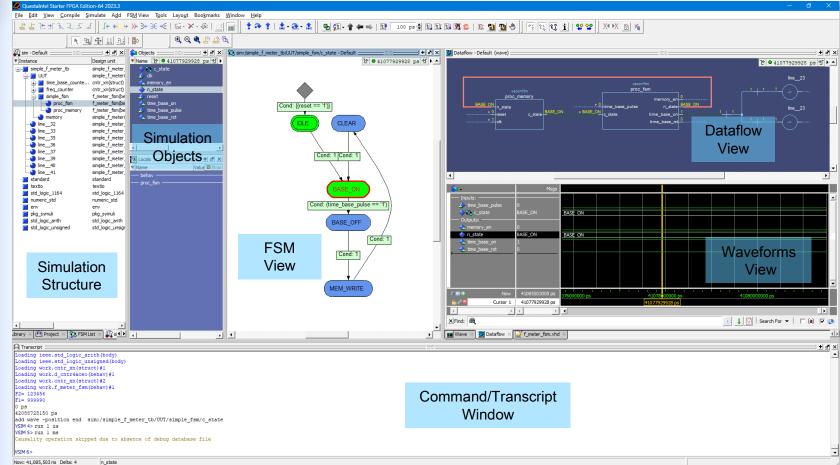

### **Questa Overview**

- Multi-language HDL simulation environment

- It can be used independently or Quartus can create startup scripts

- Two versions of the Questa\* Intel FPGA simulator available:

- Questa\* Intel® FPGA Edition

- Licenses are required and must be purchased

- 2-6X slower than Questa Core

- □ Questa\* Intel® FPGA Starter Edition

- Licenses are required but are free

- 40% slower than paid edition

- Both the free and paid editions require licenses for performing elaboration and simulation, but not for compilation

### **Questa Overview**

# **Questa Simulation Types**

| Simulation<br>Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Occurs                        |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| RTL                            | Simulation of an RTL design consisting of one or more RTL files. The RTL files can instantiate low level blocks, such as primitives, basic IP functions, and ATOMs.                                                                                                                                                                                                                                                                                          | Can perform before synthesis  |

| Post-Synthesis<br>(Gate-Level) | The Quartus EDA Netlist Writer tool generates the post-synthesis netlist. The post-synthesis netlist is a netlist of low level blocks called ATOMs. The post-synthesis netlist is a purely functional netlist.                                                                                                                                                                                                                                               | Must perform after synthesis  |

| Post-Fit<br>(Gate-Level)       | The Quartus EDA Netlist Writer can generate a Verilog HDL or VHDL gate-level netlist after the Fitter stage completes (post-fit netlist). The post-fit netlist is a netlist of ATOMs that the Fitter placed and routed on the FPGA device. The post-fit netlist is a purely functional netlist.<br><b>Note:</b> The post-fit netlist includes chip locations of ATOM instances in commented lines.<br>The post-synthesis netlist does not include this data. | Must perform<br>after fitting |

Note: The Quartus Prime software supports post-fit functional simulation, but does not support post-fit timing simulation.

# **In-System Sources and Probes (ISSP)**

- Hardware and Software Requirements

- □ Intel Quartus Prime Lite Edition

- Download Cable (USB-Blaster download cable or ByteBlaster cable)

- □ Intel FPGA development kit or user design board with a JTAG connection to device under test

- The In-System Sources and Probes Editor supports the following device families:

- Arria series

- Stratix series

- □ Cyclone series

- MAX series

- Quickly set signal to constants: pins or internal nodes

- Easily monitor signals (no-triggered continuous display)

- Works on actual hardware

- × Not-triggered might miss activity!

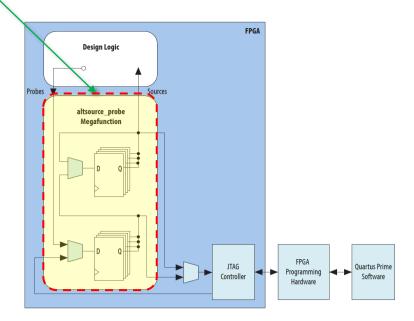

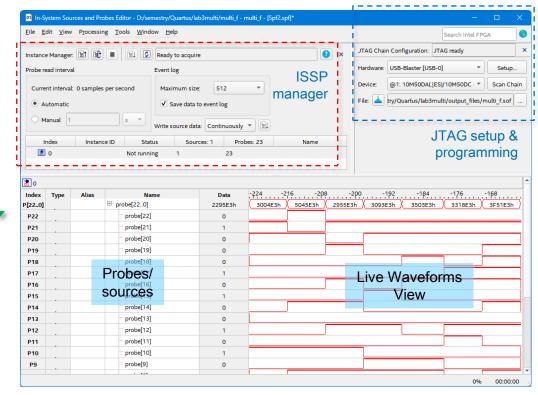

The ISSP system consists of the ALTSOURCE\_PROBE IP core and an interface to control the ALTSOURCE\_PROBE IP core instances during run time

- ISSP Editor consists of a probe function and interface to control the instances during run-time

- Allows an easy way to drive and sample signals in hardware

- Operates over JTAG

- Each ISSP instance can view/probe up to 512 signals

- Each ISSP instance can drive/source up to 512 signals

ISSP block diagram

Using In-System Sources and Probes

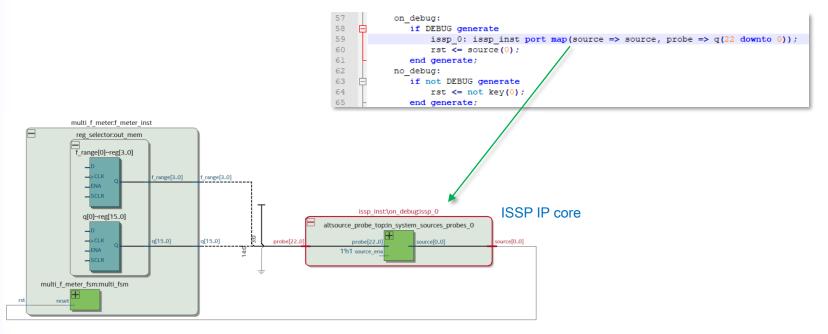

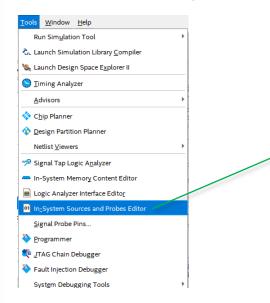

- Create ISSP IP instance using the IP Parameter Editor

- Instantiate in design and compile project

- Program target device

- Create and use ISSP Editor (.spf file) to control sources and probes

| IP Parameter Editor - issp_inst.qsys* (D\semestry\Quartus\lab3multi\issp_inst.qsys) | - O X                              |

|-------------------------------------------------------------------------------------|------------------------------------|

| <u>Eile Edit System G</u> enerate <u>V</u> iew <u>T</u> ools <u>H</u> elp           | Simulati                           |

| Nerameters 😫 – 🗗 🗆                                                                  | ) Details 🕸 🎦 Block Symbol 🕸 🗕 🗗 🗖 |

| System: issp_inst Path: in_system_sources_probes_0                                  | Show signals                       |

| Intel FPGA In-System Sources & Probes altera_in_system_sources_probes  Details      | in_system_sources_probes_0         |

| ▼ Instance Info                                                                     | sources                            |

| Vautomatic Instance Index Assignment                                                | source                             |

| Instance Index: 0                                                                   | probes                             |

| The 'Instance ID' of this instance (optional): NONE                                 | probe[220] probe                   |

| V Probe Parameters                                                                  | attera_in_system_sources_probes    |

| Probe Port Width [0512]: 23                                                         |                                    |

| Source Parameters                                                                   |                                    |

| Source Port Width [0512]: 1                                                         |                                    |

| Hexadecimal initial value for the Source Port:                                      |                                    |

| Use Source Clock                                                                    | ISSP IP core setup                 |

Using In-System Sources and Probes

- Create ISSP IP instance using the IP Parameter Editor

- Instantiate in design and compile project

- Program target device

- Create and use ISSP Editor (.spf file) to control sources and probes

Using In-System Sources and Probes

- Create ISSP IP instance using the IP Parameter Editor

- Instantiate in design and compile project

- Program target device

- Create and use ISSP Editor (.spf file) to control sources and probes

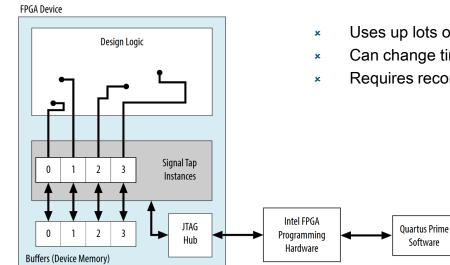

The Signal Tap Logic Analyzer captures and displays real-time signal behavior in an FPGA design using a defined clock signal

- Easily monitor signals using simple to elaborate triggering schemes  $\checkmark$

- No external equipment required  $\checkmark$

- Don't need to figure out stimulus since its based on actual hardware  $\checkmark$

- Uses up lots of memory resources inside the FPGA

- Can change timing of design

- Requires recompile witch takes time

- Hardware and Software Requirements

- □ Signal Tap Logic Analyzer (following software includes the Signal Tap):

- Intel Quartus Prime Design Software

- Intel Quartus Prime Lite Edition

- Alternatively, use the Signal Tap standalone software and standalone Programmer software

- Download Cable (USB-Blaster download cable or ByteBlaster cable)

- □ Intel FPGA development kit or user design board with a JTAG connection to device under test

- **Note**: During data acquisition, the memory blocks in the device store the captured data, and then transfer the data to the logic analyzer over a JTAG communication cable.

Opening the Standalone Signal Tap Logic Analyzer GUI

quartus\_stpw <stp\_file.stp>

# Signal Tap LA vs. External LA

- System-level debug

- Can store large quantities of data

- Flexible trigger condition

- Tap signals buried deep in the design

- No unassigned I/Os or routing needed

- Comes free with Quartus

- No external test equipment needed

- Tap new signals with the same board by recompiling, reprograming (no re-spin!)

- Create Signal Tap instance

- □ Use Signal Tap file (.stp)

- Creates a file separate from design files

- Convenient features and GUI

- Use IP Catalog

- Manually instantiate IP core directly into HDL code

- Ties the ELA to the signals directly in RTL

|                                                                                                                                                                   | 🕞 New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | × |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                                   | State Machine File<br>SystemVerilog HDL File<br>Tcl Script File<br>Verilog HDL File<br>VHDL File<br>* Memory Files<br>Hexadecimal (Intel-Format) File<br>Memory Initialization File<br>* Verification/Debugging Files<br>In-System Sources and Probes File<br>Logic Analyzer Interface File<br>Signal Tap Logic Analyzer File<br>University Program VWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|                                                                                                                                                                   | Other Files     AHDL Include File     Block Symbol File     Chain Description File     Important Security for Security Secur |   |

|                                                                                                                                                                   | × File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| o Selection Available<br>ry<br>asic Functions<br>Arithmetic<br>Bridges and Adaptors                                                                               | Cancel Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| Clocks; PLLs and Resets<br>Configuration and Programming<br>I/O<br>Miscellaneous                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| On Chip Memory<br>Simulation; Debug and Verificatio                                                                                                               | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| <ul> <li>Altera SignalTap II Log</li> <li>Altera Soft Core JTAG</li> <li>Altera Virtual JTAG</li> <li>Intel FPGA In-System</li> <li>SLD Hub Controller</li> </ul> | Sources & Probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| SLD Hub Controller Sy                                                                                                                                             | rstem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

IP Catalog

Libra

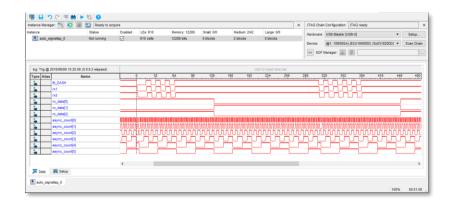

- Instance Manager

- □ Identifies which instance is being edited in the GUI

- □ Enable/disable instances quickly

- □ Gives status and resource utilization

|            | 🥍 Signal Tap Logic Analyzer - D:/s  | emestry/Quartus/la            | ab3multi/mu        | lti_f - multi_f - [stp | 1.stp]*   |           |            |            |                             |         | ×   |

|------------|-------------------------------------|-------------------------------|--------------------|------------------------|-----------|-----------|------------|------------|-----------------------------|---------|-----|

|            | <u>File Edit View Project Proce</u> | essing <u>T</u> ools <u>W</u> | (indow <u>H</u> el | lp                     |           |           |            |            | Search Intel FPGA           | ι       | ] 6 |

|            | 音 🖯 २ ९                             |                               |                    | 2                      |           |           |            |            |                             |         |     |

|            | Instance Manager: 🍳 🔎 🔳             | Add nodes                     | to the currer      | nt instance            |           |           | ×          | JTAG Chai  | n Configuration: JTAG ready |         | ×   |

|            | Instance                            | Status                        | Enabled            | LEs: 0                 | Memory: 0 | Small: NA | Medium: NA | Hardware:  | USB-Blaster [USB-0]         | Setup   |     |

|            | 🕄 auto_signaltap_0                  | Not running                   | $\checkmark$       | 0 cells                | 0 bits    | NA        | NA         | riardware. |                             | octup   | -   |

|            |                                     |                               |                    |                        |           |           |            | Device:    | @1: 10M50DA(. ES)/10M! *    | Scan Ch | ain |

| <b>.</b> . | •                                   |                               |                    |                        |           |           | Þ          | >> SOF     | Manager:                    |         |     |

- JTAG Chain Configuration

- □ Graphical setup for JTAG

- □ Buit-in Programmer

- □ Scans the JTAG chain and identifies available devices

| 🥍 Signal Tap Logic Analyzer - D:/s  | emestry/Quartus/I             | ab3multi/mu                | lti_f - multi_f - | [stp1.stp]* |           |            | - 0                                     | ×    |

|-------------------------------------|-------------------------------|----------------------------|-------------------|-------------|-----------|------------|-----------------------------------------|------|

| <u>File Edit View Project</u> Proce | essing <u>T</u> ools <u>V</u> | <u>/</u> indow <u>H</u> el | p                 |             |           |            | Search Intel FPGA                       |      |

| २ 🗧 🗄 🤰                             |                               |                            | ?                 |             |           |            | ,                                       |      |

| Instance Manager: 🍳 👂 🔳             | Add nodes                     | to the currer              | nt instance       |             |           | ×          | JTAG Chain Configuration: JTAG ready    | ×    |

| Instance                            | Status                        | Enabled                    | LEs: 0            | Memory: 0   | Small: NA | Medium: NA | Hardware: USB-Blaster [USB-0] 🔻 Setup   |      |

| 🔝 auto_signaltap_0                  | Not running                   | $\checkmark$               | 0 cells           | 0 bits      | NA        | NA         |                                         |      |

|                                     |                               |                            |                   |             |           |            | Device: @1: 10M50DA(. ES)/10M! 🔻 Scan C | hain |

|                                     |                               |                            |                   |             |           |            | >> SOF Manager: 👗 🕕                     |      |

| •                                   |                               |                            |                   |             |           | Þ          |                                         |      |

|                                     |                               |                            |                   |             |           |            |                                         |      |

- Nodes List

- □ Use the Node Finder to add signals to be tapped

- □ Automatically groups busses together and create custom groups

|                               |                                                                                                                      | Lock mode:  | Allow all char | 1                  | Signal Configuration: X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | Node                                                                                                                 | Data Enable | Trigger Enable | Trigger Conditions | Clock: adc_clk_10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ype Alias                     | Name                                                                                                                 | 17          | 17             | 1 ✓ Basic AND ▼    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               | meter_inst reg_selector:out_mem q[0]                                                                                 | <b>v</b>    | ✓              |                    | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <u> </u>                      | meter_inst reg_selector:out_mem q[1]                                                                                 | <b>v</b>    | <b>v</b>       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>►</b>                      | meter_inst reg_selector:out_mem q[2]                                                                                 |             | ✓              |                    | Sample depth: 512 TRAM type: Auto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <u></u>                       | meter_inst reg_selector:out_mem q[3]                                                                                 | V           | ✓              |                    | Segmented: 2 256 sample segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <u> </u>                      | meter_inst reg_selector:out_mem q[4]                                                                                 | <b>v</b>    | ✓              |                    | Segmented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| R                             | meter_inst reg_selector:out_mem q[5]                                                                                 | V           | <b>v</b>       |                    | Nodes Allocated:  Auto Manual: 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>₿</b>                      | meter_inst reg_selector:out_mem q[6]                                                                                 |             | <b>v</b>       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| R                             | meter_inst reg_selector:out_mem q[7]                                                                                 | V           | V              |                    | Pipeline Factor: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R I I                         | meter inst/reg selector.out mem/q[8]                                                                                 | <b>v</b>    | $\checkmark$   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               | meter_instrieg_selector.out_memiq[0]                                                                                 |             |                |                    | Storage qualifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |