Embedded Systems Hardware Design

## **Memory subsystems**

001000111001110100000011110010001010100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100

#### **Memory subsystem**

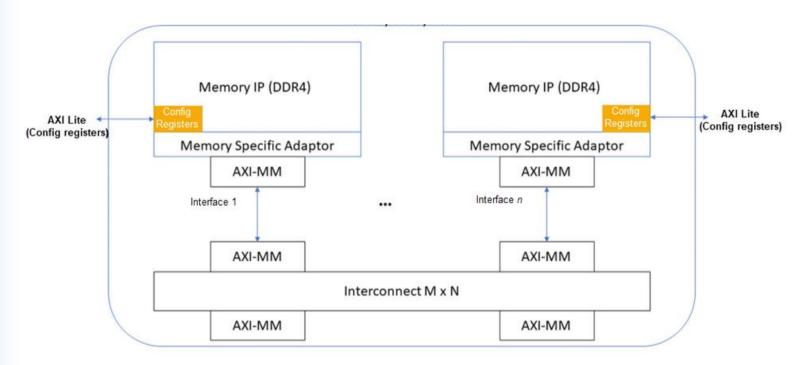

The memory subsystem IP is a high-level solution on top of the External Memory Interfaces.

Source https://www.intel.com/content/www/us/en/docs/programmable/789389/24-1-2-0-0/introduction-to-memory-subsystem-ip.html

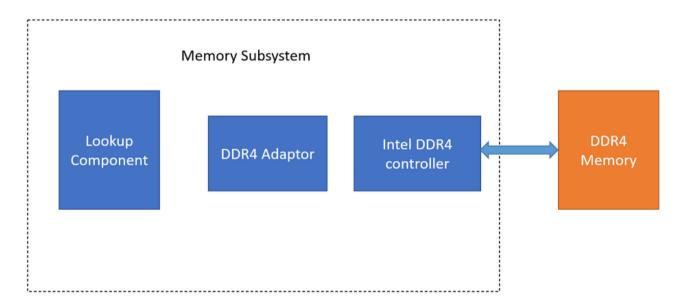

# Memory Subsystem IP Used as Memory Adaptor with Lookup and One EMIF

The memory subsystem IP can be configured for use in various applications such as full crossbar for machine learning, multi-hierarchy memory bridge, or as a memory-specific adaptor with lookup core logic. All the available modes offer common scalability and compose-ability.

Source https://www.intel.com/content/www/us/en/docs/programmable/789389/24-1-2-0-0/introduction-to-memory-subsystem-ip.html

#### **Types**

- ROM

- PROM

- EPROM

- EEPROM

- RAM

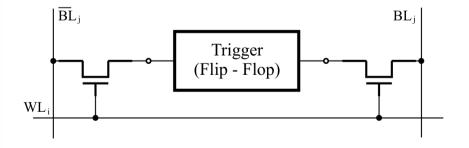

- SRAM

- DRAM

- Synchronous

- DDR Double data rate

- NVRAM (non-volatile RAM)

#### Static RAM

- Uses SR-Latches

- Expensive

- Doesn't need refreshing

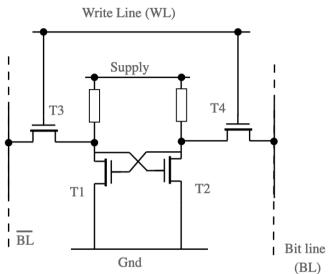

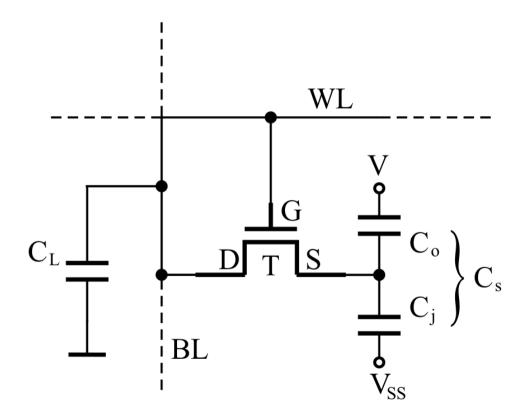

## Dynamic RAM

- Uses small capacitors (with transistors)

- Requires constant refreshing

- Cheap

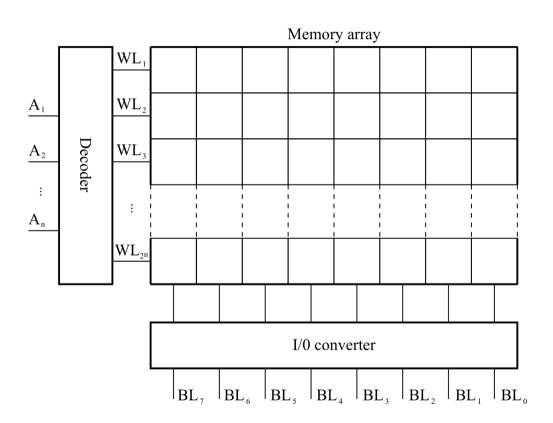

## Digital memory architecture

#### Max supported memory & the '4GB limit'

- Address lines ~ Bits

- 16 bit => 216 = 65,536 bytes (64 KiB)

- 32 bit => 232 = 4,294,967,296 bytes (4 GiB)

- 64 bit => 264 = 18,446,744,073,709,551,616 bytes (16 EiB)

- KiB ≠ KB, GiB ≠ GB, EiB ≠ EB

- KB, MB, GB, PB, EB 1000 as a base

- KiB, MiB, GiB, PiB, EiB 1024 as a base

- 1 MB = 0.953 MiB

- 1.073 TB = 1 TiB

#### PAE

- Physical address extension

- Allows 32-bit OS to address more than 4GiB of memory

- From 2<sup>32</sup> to 2<sup>36</sup> bytes

- Requires OS, CPU and motherboard chipset support.

- e.g. 32bit OS Windows Server 2008 Enterprise, Datacenter can address up to 64

GB of memory

#### **RAM**

- RAM Random Access Memory

- DRAM Dynamic RAM

- SRAM Static RAM

- SDRAM Synchronous DRAM

- DDR Double Data Rate (data is transferred on both rising and falling edges of the system's memory clock)

## (S)DRAM

- SDR SDRAM (Single Data Rate)

- DDR SDRAM (Double Data Rate)

- DDR2 SDRAM

- DDR3 SDRAM

- DDR4 SDRAM

- DDR5 SDRAM

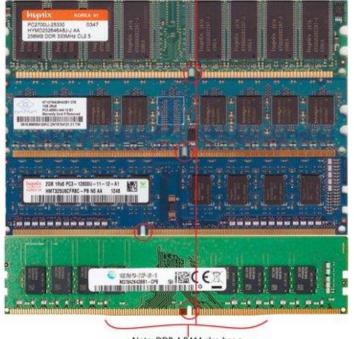

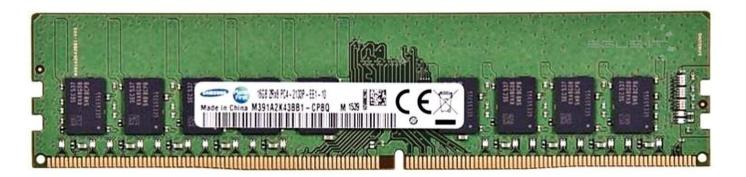

#### **Formfactors**

- DIMM Dual In-Line Memory Module

- SODIMM Small Outline DIMM

- CAMM/LPCAMM Compression Attached Memory Module

- Soldered

## Physical Differences DDR 1, 2, 3, 4 DIMMS

**184 PINS**

**240 PINS**

**240 PINS**

**288 PINS**

DDR 1

DDR 2

DDR 3

DDR 4

Note: DDR 4 RAM also has a slight bow in the row of pins.

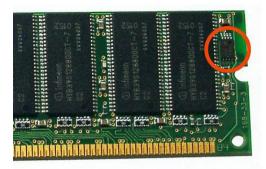

# SODIMM

DIMM

SO-DIMN

Every standard (SDRAM, DDR{1..5}) has its own SODIMM version - notch in different spots

#### DDR3 240/204pin Converter

DDR3 240pin DIMM Pin-out

SODIMM can be used in DIMM slot using an adapter - same signals, different form-factor

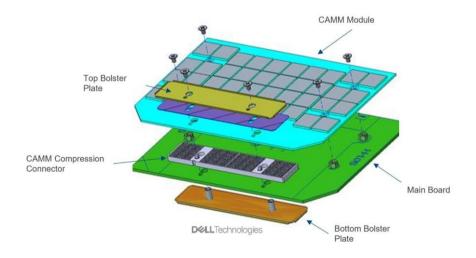

#### CAMM

- Thinner than SODIMM (~57% thinner)

- Shorter traces (can be faster)

- Replacable/upgradable (vs soldered RAM)

Source: https://www.extremetech.com/computing/334676-dell-offers-additional-insight-on-its-new-camm-memory-modules

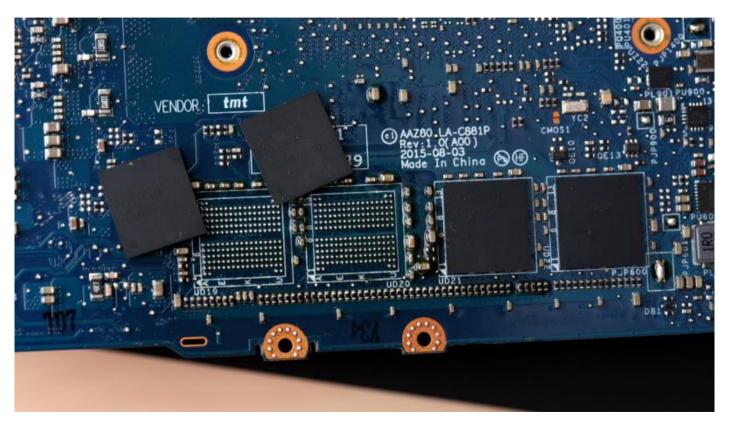

#### Soldered

Source: https://hackaday.com/2021/11/24/you-cant-upgrade-soldered-on-laptop-ram-think-again/

## Voltage

- . DDR (2.6V, 2.5V)

- DDR2 (1.8V)

- DDR3 (1.5V), DDR3L (1.35V)

- DDR4 (1.2V), <del>DDR4L (1.05V)</del>

- DDR5 (1.1V)

#### DDR3L

- Lower required voltage less power consumption

- Can work at both 1.35V and 1.5V (compatible with systems using DDR3 not 'L')

- Some systems doesn't work with DDR3 and require DDR3L

#### **LPDDR**

- Low power DDR

- Aimed at mobile devices

- DDR3L vs LPDDR3

- LPDDR4(x)

- LPDDR5(x)

- LPDDR6 ~2024/2025

#### Properties of the different LPDDR generations

| LPDDR                                                | 1               | 1 <u>E</u> | 2                   | 2 <u>E</u> | 3          | 3E   | 4           | 4X                  | 5                    | 5X                   |

|------------------------------------------------------|-----------------|------------|---------------------|------------|------------|------|-------------|---------------------|----------------------|----------------------|

| Maximum density (bit)                                |                 |            |                     |            | 32         |      | 64          | 64                  | 32                   | 32                   |

| Memory array<br>clock (MHz)                          | 200             | 266        | 200                 | 266        | 200        | 266  | 200         | 266                 | 400                  | 533                  |

| Prefetch size                                        | 2 <i>n</i>      |            | 4 <i>n</i>          |            | 8 <i>n</i> |      | 16 <i>n</i> |                     |                      |                      |

| Memory<br>densities                                  |                 |            | 64 Mbit –<br>8 Gbit |            | 1–32 Gbit  |      | 4–32 Gbit   |                     | 4–32 Gbit            |                      |

| I/O bus clock<br>frequency<br>(MHz)                  | 200             | 266        | 400                 | 533        | 800        | 1067 | 1600        | 2133                | 3200                 | 4267                 |

| Data transfer<br>rate, DDR (MT/<br>s) <sup>[a]</sup> | 400             | 533        | 800                 | 1067       | 1600       | 2133 | 3200        | 4267                | 6400                 | 8533                 |

| Supply voltages (volts)                              | 1.8             |            | 1.2, 1.8            |            | 1.2, 1.8   |      | 1.1,<br>1.8 | 0.6,<br>1.1,<br>1.8 | 0.5,<br>1.05,<br>1.8 | 0.5,<br>1.05,<br>1.8 |

| Command/<br>address bus                              | 19 bits,<br>SDR |            | 10 bits             |            | , DDR      |      | 6 bits, SDR |                     | 7 bits, DDR          |                      |

| Year                                                 | 2006            |            | 2009                |            | 2012       |      | 2014        | 2017                | 2019                 | 2021                 |

#### LPDDR in Samsung phones

- S23 (2022) LPDDR5X

- S21 (2020) LPDDR5

- . S10 (2019) LPDDR4X

- . S7 (2016) LPDDR4

- . S5 (2014) LPDDR3

- S2 (2011) LPDDR2

#### **Types**

- UDIMM unbuffered/unregistered DIMM

- Most consumer memory

- Rarely with ECC

- RDIMM Registered DIMM

- Additional register chip (buffer) is added between DRAM chips and MC.

- Allows for more DRAM chips on one DIMM (reduces electrical load on the control lines)

- Usually has ECC capabilities

- LRDIMM Load Reduced DIMM

- Similar to RDIMM, but also data lines are buffered

#### **ECC** memory

- ECC Error correction codes

- Used to detect and fix memory errors

- Protects against 'bit-flips'

- 1-bit errors are detected and are transparently corrected

- 2-bit errors are detected and cannot be corrected

#### Systems' memory requirements

- Some platforms require the use of RDIMM

- Since DDR5: RDIMM is keyed differently to UDIMM

- UDIMM platform cannot use RDIMM

- Non-ECC UDIMM plaforms can still use ECC UDIMMs

- To use ECC of UDIMM CPU and Chipset need to support ECC features.

#### UDIMM - ECC vs non-ECC

Aditional register chip (buffer) in the middle of a module

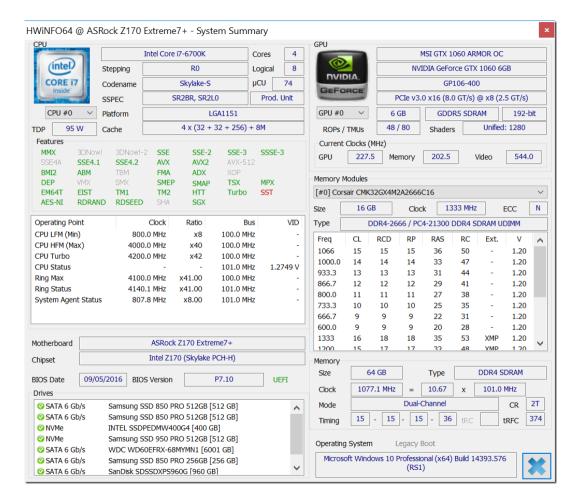

#### Supported Memory Type for Intel Core Desktop Processors

- DDR3: 1st 7th gen

- DDR4: 6th 14th gen

- DDR5: 12th 14th gen

- Most CPUs support two memory standards

- Only one can be used at one time

- Different motherboards can use different memory type for the same CPU

- https://www.intel.com/content/www/us/en/support/articles/000094585/proce ssors.html

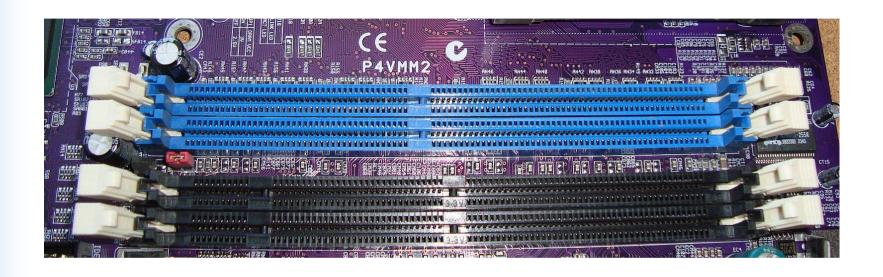

#### Motherboards with two memory types

SDRAM and DDR(1) slots on P4VMM2 Only one type can be used at once (or it doesn't POST)

#### **GDDR SDRAM**

- GDDR Graphics Double Data Rate SDRAM

- DDR SGRAM

- GDDR2

- GDDR3

- GDDR4

- GDDR5

- GDDR6

- GDDR7

#### Detection

- SPD Serial presence detection

- Simply flash memory (EEPROM)

- Uses SMBUS (~l<sup>2</sup>C, also for temp. sensors on DIMMs)

- Contains: model name, specifications, supported timings, (optionally) XMP timings (Extreme Memory Profile)

- JEDEC Standard 21-C section 4.1.2.4 "SPDs for DDR SDRAM"

#### Memory training

- MRC Memory reference code

- Q: How to run code (MRC) when memory is not yet available?

- A: Use CAR 'Cache as RAM'

#### Memory controller

- In the past: dedicated chip (integrated in north bridge)

- Present: integrated into CPU-package

- Called IMC (Integrated Memory Controller)

- Responsible for refreshing memory cells

- Takes the memory address as an input and fetches/writes data from/to main memory (DRAM).

- Usually integrated with MMU (memory management unit)

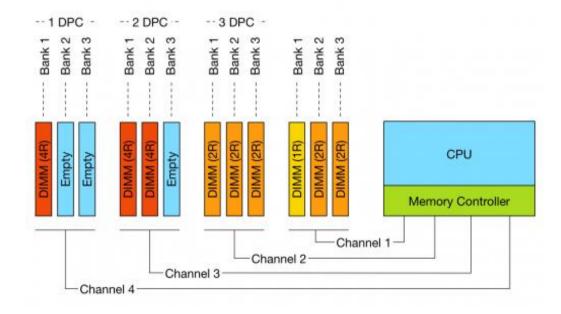

#### Multi-channel memory architecture

- MC has to support additional channels

- Requires specific memory configuration

- At least two modules for Dual-Channel

- Three for Triple-Channel, four for Quad-Channel

- Some implementations allow for 'Flexible mode'

- different modules' capacity

- Dual/Triple/Quad-Channel interleaved

- spreads the data among different modules

- allows for greater speeds

- DDR5 has additionally introduced sub-channels

#### Multi-Channel, multi-dimm

- . DPC

- DIMMs per channel

- MC can use only one DIMM in a channel at the same time

#### Attacks/mitigations

- Cold-boot attacks

- Rowhammer

- Memory scrambling

- Intel's Total Memory Encryption

- Memory scrubbing

- ECC

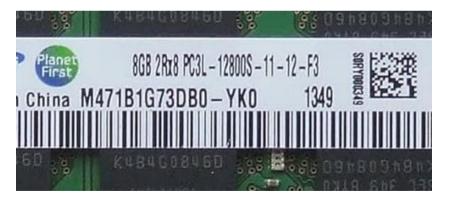

#### Memory timings

- CL CAS Latency

- CAS = Column Address Strobe

- T<sub>RCD</sub> Row Address to Column Address Delay

- T<sub>RP</sub> Row Precharge Time

- T<sub>RAS</sub> Row Active Time (Row Address Strobe)

- Usually presented in 'number of clock-cycles'

#### Memory timings

- Format: XX-XX-XX

- 1) CL

- 2) tRCD

- 3) tRP

- 4) tRAS

- Some can be ommited

- CL=11, tRCD=12

- F3 is manufacturer specific info

- Note: 12800S => 1600Mhz

## **Combining Memory modules**

- To make word larger

- To add more address lines

#### Additional materials

- https://www.atpinc.com/blog/DDR5-dimm-types-rdimm-vs-udimm-for-server-platform

- https://frankdenneman.nl/2015/02/18/memory-tech-primer-memory-subsystemorganization/

- https://www.youtube.com/watch?v=7J7X7aZvMXQ